PLA

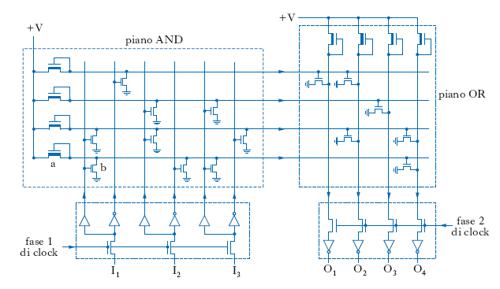

Sigla di programmable logic array, che in microelettronica indica un insieme di transistori disposti a matrice in un circuito integrato e opportunamente connessi a un fascio di linee di ingresso e di uscita, in modo da realizzare una complessa funzione logica. Un modo molto generale per realizzare circuitalmente una funzione logica combinatoria a n ingressi e m uscite, che dà luogo inoltre a una struttura di lay-out molto regolare, è quello di usare una memoria (per es., una ROM) di 2n parole, ciascuna di m bit; gli n ingressi formano un indirizzo per la memoria e le m uscite sono proprio i dati contenuti nella locazione di memoria indirizzata: questa memoria realizza la tavola della verità completa per le funzioni di uscita. La PLA è una struttura con tutta la generalità di una memoria, tuttavia una specifica struttura PLA contiene solo una riga di elementi circuitali per ciascuno dei termini di prodotto necessari per realizzare una data funzione logica ed è quindi molto più compatta di una ROM logicamente equivalente. La fig. illustra la struttura complessiva della PLA. Gli ingressi, I1, I2 e I3, memorizzati durante la prima fase di un clock a due fasi, e i loro complementi sono trasportati, mediante un fascio di linee conduttrici verticali, all’interno di una prima matrice di transistori detta piano AND: questo piano genera opportune combinazioni logiche degli ingressi e dei loro complementi. Le uscite del piano AND sono raccolte e trasportate come ingressi, mediante un fascio di linee conduttrici orizzontali, all’interno di una seconda matrice di transistori, detta piano OR. Anche questo piano genera opportune combinazioni logiche delle uscite del piano AND. Un fascio di linee conduttrici verticali trasporta le uscite del piano OR verso un registro di uscita nel quale sono memorizzate durante la seconda fase del clock e rese disponibili sotto forma di complementi O1, O2, O3 e O4 all’uscita della PLA. Come si può notare nello schema circuitale mostrato in fig., in ciascuno dei due piani AND e OR sono presenti delle linee conduttrici connesse al livello logico alto V mediante un transistore a, detto pull-up: lungo la linea sono opportunamente disposti alcuni transistori b, detti pull-down, che, in relazione al valore logico dell’ingresso connesso al loro gate, possono invece portare la linea al livello logico basso. La realizzazione della funzione logica da attuare con la PLA consiste proprio nel disporre opportunamente, all’interno dei piani AND e OR, i transistori pull-down.