Microelettronica

Microelettronica

Le moderne tecnologie informatiche, delle telecomunicazioni, dei sistemi di controllo, e tutte le relative applicazioni, trovano le loro basi nello sviluppo e nella disponibilità a basso costo dei circuiti integrati (Integrated Circuit, IC o anche chip), dispositivi elettronici di elevatissima complessità, realizzati in forma estremamente compatta e miniaturizzata. Tali dispositivi sono anche detti microcircuiti, mentre con microelettronica si indica il settore dell'ingegneria che si occupa della loro progettazione e realizzazione.

La m. fonda le sue basi, fisiche e concettuali, nell'invenzione, avvenuta negli anni Quaranta, del transistore, che, già negli anni Cinquanta, ha trovato le sue prime importanti applicazioni di largo consumo nei piccoli radioricevitori noti, a quel tempo, come radio a transistori o anche, semplicemente, all'ingl., transistor. Le prime applicazioni, pur apparendo allora rivoluzionarie (i precedenti radioricevitori a tubi termoelettronici, o 'a valvole', erano di gran lunga più ingombranti e non potevano funzionare con l'alimentazione a pile), utilizzavano solo pochissimi transistori, tipicamente in numero inferiore a dieci e realizzati singolarmente. A distanza di cinquant'anni, dopo che si è imparato a costruire circuiti integrati contenenti molte migliaia di transistori, non si sono ancora raggiunti i limiti della densità e del numero totale di transistori che ciascun circuito può contenere: alla fine degli anni Novanta si è arrivati a costruire infatti dispositivi contenenti fino a dieci milioni di transistori, caratterizzati da funzionalità esterne estremamente complesse (per es. in termini di funzioni logiche eseguibili) e tali da consentire lo sviluppo delle applicazioni più varie e più impensate. Quando si utilizza un'agenda elettronica tascabile, un telefono cellulare, un piccolo elaboratore portatile, è necessario tener presente che, nel loro interno, uno o più circuiti integrati, contenenti ciascuno varie decine di migliaia di transistori, ne permettono il funzionamento e ne sostengono le funzionalità logiche esterne, che l'utilizzatore impara a usare senza necessariamente conoscere le complesse funzioni logiche interne ai dispositivi stessi.

La realizzazione dei microcircuiti ha dato luogo a due tendenze fondamentali: la prima riguarda la miniaturizzazione dei componenti (un singolo transistore all'interno del chip occupa una superficie pari a piccole frazioni di μm²), la seconda riguarda la possibilità di implementare funzionalità estremamente complesse, sulla base della logica binaria (costituita dagli stati elementari 0 e 1). L'uso di tale logica permette altresì di rappresentare ed elaborare i segnali e le grandezze d'interesse, secondo la tecnica digitale (o numerica), che consiste nell'acquisire, trasmettere e trasformare sequenze numeriche binarie e nell'eseguire su di esse operazioni aritmetiche di vario tipo e complessità. Tutti gli elaboratori elettronici funzionano su tali principi e sul fatto che le singole operazioni elementari possono essere svolte in intervalli di tempo estremamente brevi (dell'ordine dei ns).

La m. si occupa di tutti i problemi inerenti i microcircuiti, dalla loro progettazione al loro collaudo. Spesso l'insieme dei microcircuiti e degli altri dispositivi di supporto viene indicato come l'hardware di un'apparecchiatura, in quanto, a causa della grande complessità, vari tipi di funzioni possono essere ottenuti e sviluppati per mezzo del software, e cioè programmando il funzionamento dei dispositivi stessi. Così un singolo dispositivo integrato può funzionare in molti modi diversi, a seconda di come viene programmato.

La m. ha avuto un forte impatto non solo nel campo tecnico, ma anche in quello economico e sociale. Infatti, anche se inizialmente l'obiettivo primario della m. era costituito dalla riduzione di massa e di ingombro dei circuiti elettronici, come richiesto da alcune applicazioni particolari (quali, per es., i circuiti dei satelliti per telecomunicazioni o delle sonde spaziali), in seguito hanno assunto importanza predominante gli effetti indotti, quali l'aumento di affidabilità e la riduzione del costo. La disponibilità di circuiti affidabili, poco ingombranti e poco costosi ha reso possibile la costruzione, l'efficace funzionamento e l'offerta a prezzi accessibili dei personal computer, elaboratori di largo consumo equivalenti, a distanza di solo un decennio, a precedenti elaboratori d'uso specialistico e di grande potenza. I progressi della tecnologia sono stati tali da consentire la messa a punto di mezzi di calcolo le cui possibilità sono sfruttate solo parzialmente, in attesa di adeguati sviluppi nel campo delle interfacce uomo-macchina, dei sistemi operativi e degli algoritmi di elaborazione. Appare quindi capovolta la situazione che si aveva negli anni Sessanta, quando lo sviluppo di alcuni settori applicativi era limitato da una tecnologia non ancora matura. I dispositivi realizzabili con le tecnologie disponibili sono così complessi che anche un singolo microcircuito non può essere progettato manualmente: pertanto, la progettazione nel campo della m. è effettuata con mezzi e procedure automatizzate denominate CAD (Computer Aided Design). La fase di progettazione con mezzi CAD precede la realizzazione fisica dei microcircuiti, effettuata in apposite industrie (foundry), nelle quali è disponibile ed è eseguito il processo tecnologico. Di conseguenza il progettista, dopo aver sviluppato su elaboratore il proprio progetto, simulandone il comportamento a vari livelli, genera un insieme di dati (file o stream) che, inviato alla foundry, consente la fabbricazione pressoché automatica del chip. La separazione delle fasi di progetto e di costruzione effettiva dei circuiti integrati rende accessibile la realizzazione e l'applicazione di microcircuiti anche presso laboratori e industrie che non posseggono il processo tecnologico.

La m. ha avuto inizio quando è apparso possibile realizzare più componenti sullo stesso chip. Le prime realizzazioni significative risalgono al 1958 a opera di J.S. Kilby, presso la società Texas Instruments. I primi microcircuiti erano in tecnologia bipolare; in seguito sono stati introdotti microcircuiti di tipo MOS (Metal Oxide Semiconductor) e CMOS (Complementary MOS) che hanno largamente dominato nella maggior parte delle applicazioni (v. oltre: Tecnologie planari su silicio). Un parametro significativo per valutare lo sviluppo della m. nel corso degli anni è costituito dal numero massimo di transistori realizzabili nel singolo chip. Il progresso in tal senso ha modificato la scala d'integrazione dei microcircuiti (SI, Scale Integration). Le tappe significative sono state: il superamento dei 100 transistori per chip nel 1965 (con il passaggio dalla SSI, Small SI, alla MSI, Medium SI); il superamento dei 1000 transitori per chip nel 1970, con l'inizio della larga scala d'integrazione (LSI, Large SI); infine, l'avvento della larghissima scala d'integrazione nel 1979 con il superamento dei 100.000 transistori per chip (VLSI, Very Large SI). In seguito sono stati realizzati microcircuiti con più di un milione di transistori, e la limitazione a ulteriori sviluppi è risultata più progettuale che tecnologica. Negli anni Novanta, con l'avvento delle tecnologie capaci di realizzare singoli transistori di dimensioni inferiori al micron di metro, si è iniziato a produrre microcircuiti con più di 10 milioni di componenti; in questo caso, si definisce una scala d'integrazione ultra larga (ULSI, Ultra Large SI). Nei riguardi della scala d'integrazione si è osservato che per circa un quindicennio, a partire dai primi anni Ottanta, il progresso nelle capacità di integrazione è risultato quantificabile con un raddoppio, ogni anno, del numero massimo di transistori realizzabile per circuito integrato (v. elaboratori elettronici, in questa Appendice). Notevoli progressi hanno anche riguardato la massima frequenza d'impiego dei microcircuiti, la quale è andata aumentando e ha dato luogo allo sviluppo di diverse tecnologie specifiche (tecnologia del silicio fino a circa 1 GHz, tecnologia dell'arseniuro di gallio nel campo delle microonde). Dal punto di vista del tipo di segnali elettrici utilizzati nei microcircuiti, si distinguono le realizzazioni di tipo digitale da quelle di tipo analogico, risultando le prime di gran lunga più sviluppate delle seconde. In effetti, lo sviluppo della m. ha in gran parte coinciso con l'affermazione delle tecniche digitali negli elaboratori, nelle telecomunicazioni e nei sistemi di controllo. Peraltro, con il crescere della scala d'integrazione, sono stati prodotti dispositivi sempre più complessi nel campo delle memorie per elaboratori, delle unità di calcolo e delle interfacce. Sono stati in tal modo prodotti microcircuiti destinati ad ampi campi applicativi (Commodity IC), che, per es., hanno largamente condizionato gli sviluppi e il mercato mondiale degli elaboratori. D'altra parte i progressi nel VLSI hanno reso possibile lo sviluppo di apparati complessi per specifiche applicazioni su pochi (al limite, su un solo) chip altamente specializzati, progettati appositamente e di proprietà di un'unica industria committente (ASIC, Application Specific IC).

Aspetto e funzionalità esterne dei microcircuiti

I singoli microcircuiti sono normalmente installati all'interno dei dispositivi su apposite schede elettroniche (circuiti stampati, board). In genere, ciascuna scheda non contiene molti chip e può a volte apparire anche relativamente semplice, grazie al fatto che la complessità risulta confinata all'interno di ciascun chip. Inoltre, anche per numeri di transistori interni al chip molto elevati, il numero delle connessioni esterne (dette pin) non può superare certi valori (al massimo qualche centinaio). È proprio tale numero di pin che stabilisce il tipo e le dimensioni esterne dell'integrato, ovvero del suo contenitore (case). I vari cases appartengono a poche tipologie, a seconda del numero e della posizione dei pins (pin-out), della loro forma e del materiale con cui sono realizzati. Il circuito integrato effettivo si trova incapsulato all'interno del case e, in genere, ne occupa solo una piccola parte di forma rettangolare. Tale circuito, oltre ai componenti costitutivi interni, contiene lungo il perimetro esterno una fila di contatti, detti pad, in numero uguale ai pins esterni e a questi connessi per mezzo di sottilissimi conduttori. L'incapsulamento e la connessione dei microcircuiti all'interno del case sono effettuati presso la foundry o presso altra ditta specializzata. I pins esterni sono in diretto contatto elettrico con i pads del chip. Pertanto, tenendo conto dei livelli di impedenza dei circuiti interni al chip e dei componenti presenti, è necessario maneggiare l'integrato con estrema cautela, in quanto il semplice contatto (per es. con le mani) dei pins può provocare accumuli di cariche elettriche tali da danneggiare il dispositivo. Pertanto i circuiti integrati, quando non sono ancora montati sul circuito stampato, sono sempre protetti da opportuni contenitori antistatici. Il costruttore, in genere, fornisce le caratteristiche esterne del circuito integrato, e cioè il modo con cui dev'essere alimentato elettricamente, e le funzionalità accessibili dai vari pins, comprese le necessarie temporizzazioni dei segnali. Queste informazioni occorrono al progettista della scheda elettronica per scegliere tutti i circuiti necessari per realizzare il cablaggio, per stabilire le caratteristiche elettriche del dispositivo e le funzionalità logiche. D'altra parte è evidente che, senza le informazioni del costruttore, sarebbe estremamente difficile, se non impossibile, trarre tali informazioni attraverso misure o prove sui pins esterni. Nello stesso modo è assolutamente impossibile dedurre come il circuito integrato sia costruito internamente, senza le opportune informazioni, in particolare se questo è di tipo ASIC. Pertanto lo sviluppo di circuiti integrati ASIC, pur dispendioso, rappresenta una garanzia per il costruttore contro la possibilità di realizzazione di copie non autorizzate.

Una classificazione dei circuiti ASIC è impossibile, poiché essi sono realizzati in vista di particolari applicazioni. Per gli integrati di uso generale, invece, si può tentare una classificazione a grandi linee, essendo questi realizzati in vista di applicazioni di tipo non specifico.

Nel campo dei dispositivi digitali, si possono così considerare i circuiti logici (da pochi elementi, fino a matrici logiche estese), i circuiti logici programmabili (FPGA, Field Programmable Gate Array), i microprocessori, i circuiti per il processamento del segnale (DSP, Digital Signal Processors) ecc. Un discorso a parte dev'essere fatto per le memorie integrate, per le quali è spesso utilizzato un processo tecnologico specifico. Occorre notare che, nella realizzazione di un ASIC, le funzionalità e gli schemi di vari chip di tipo più elementare possono essere usati come sottosistemi complessi (detti macrocelle), all'interno del dispositivo integrato. Così possono essere costruiti circuiti aventi nell'interno un microprocessore, della memoria, della logica specifica, a seconda delle esigenze. Alcuni chip possono essere programmati in forma stabile, attraverso opportuni segnali elettrici esterni, e successivamente la loro programmazione può essere cancellata attraverso l'esposizione del chip a opportune fonti di energia (tipicamente a raggi ultravioletti). In tali chip, il case è realizzato con un'opportuna finestra trasparente che permette di effettuare l'opportuno processo di esposizione delle zone sensibili in fase di cancellazione.

Nel campo dei dispositivi analogici, sono realizzati circuiti integrati che svolgono le funzioni di amplificazione, di filtraggio, di equalizzazione. Tali tipi di chip devono essere classificati in base ai livelli di potenza, di segnale e di frequenza desiderati. Chip particolari, indicati spesso con il nome di circuiti monolitici, sono utilizzati nel campo delle microonde.

Tecnologie planari su silicio

La m. si è sviluppata dopo l'invenzione del transistore bipolare a giunzione (BJT, Bipolar Junction Transistor), quando è apparso chiaro che la tecnologia di fabbricazione consentiva di costruire più transistori sullo stesso chip con un unico processo chimico-fisico. Successivamente è stata sviluppata la tecnologia MOS, adatta a realizzare transistori a effetto di campo MOSFET (MOS Field Effect Transistor), che hanno vari vantaggi rispetto ai transistori BJT, fra cui quello di richiedere un minor consumo di potenza durante il funzionamento (v. transistore, App. V). Attualmente la tecnologia MOS è preferita rispetto a quella bipolare nella maggioranza delle applicazioni.

Per descrivere in dettaglio i passi necessari per la realizzazione di un circuito integrato è pertanto utile fare riferimento a un processo di fabbricazione tipico, messo a punto per la tecnologia CMOS, con la quale possono essere realizzati sia transistori MOS a canale p, sia transistori MOS a canale n (v. anche elettronica, memoria: Elettronica, semiconduttori, App. V).

I passi fondamentali del processo tecnologico, che sono messi a punto nelle singole foundries, sono estremamente complessi e devono essere realizzati in opportuni laboratori nei quali la temperatura, l'umidità, le impurezze presenti sono strettamente controllate. Fra di essi è opportuno citare: la realizzazione del substrato, la mascheratura, il processo fotolitografico, la deposizione, l'attacco, la diffusione, l'accrescimento epitassiale e l'ossidazione.

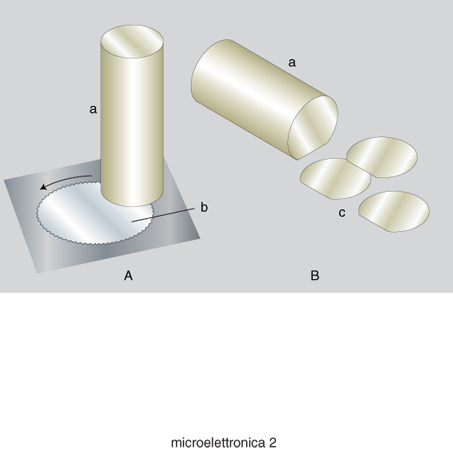

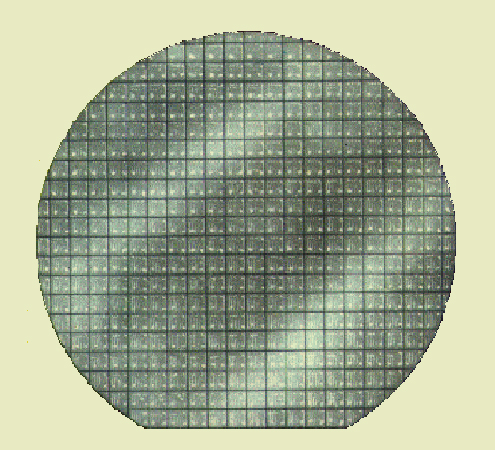

Il substrato. - Detto anche lastrina o fetta (wafer), è il supporto sul quale sono realizzati i circuiti integrati. Dallo stesso wafer possono essere ottenuti, mediante taglio, parecchi chip, a seconda della complessità dei circuiti e della dimensione del wafer, il quale è ricavato da un unico monocristallo cilindrico di silicio, leggermente drogato con impurità di tipo p o n, mediante tagli perpendicolari all'asse del cilindro stesso (fig. 2). I wafers sono spessi da 250 μm a 400 μm. Spessori più sottili, anche se ancora accettabili da un punto di vista elettrico, comporterebbero un'eccessiva fragilità meccanica. Il diametro delle lastrine è andato aumentando con il tempo ed è passato dai 4 pollici agli attuali 8 pollici. Questo perché, col progredire della tecnologia di fabbricazione, si è riusciti a garantire l'omogeneità delle varie fasi di fabbricazione su aree più grandi, con il vantaggio di poter realizzare più chip sulla stessa fetta. La funzione del substrato è duplice, sia come sostegno meccanico, sul quale viene realizzato il circuito, sia come parte attiva del circuito stesso.

Le maschere. - Sono strutture di vario tipo che permettono di trasferire sul substrato le geometrie che definiscono i vari tipi di circuiti, di componenti e le loro interconnessioni. Esse sono tipicamente realizzate in vetro, ricoperto da un sottile strato di metallo opaco, in modo da riprodurre la particolare geometria che rappresenta il circuito. Ci sono differenti metodi per realizzare le maschere. Un primo metodo, impiegato molto diffusamente in passato, ma attualmente in disuso, impiega un processo di riduzione fotografica a partire da un disegno, in scala, ma di dimensioni molto maggiori. Attualmente è invece utilizzato un fascio di luce laser, che, asservito a un elaboratore, effettua la scansione di tutta l'area interessata e impressiona la maschera come una pellicola fotografica; tale metodo, come il precedente, deve tuttavia fare uso di un processo di riduzione per arrivare alla dimensione desiderata. L'impressionamento diretto della maschera nella sua dimensione ridotta definitiva può essere invece ottenuto utilizzando la scansione di un fascio di elettroni E-Beam (Electron Beam). Quest'ultimo metodo, a scapito dell'alto costo dell'apparecchiatura, permette di produrre maschere di qualità elevata e viene utilizzato per geometrie di dimensioni molto ridotte.

Il processo fotolitografico. - È il procedimento che permette di trasferire sul substrato le informazioni geometriche presenti sulle maschere. A tale scopo, un particolare liquido, chiamato fotoresist e sensibile alla luce (raggi ultravioletti o raggi X), è applicato sul substrato in un sottile strato uniforme di circa 1 μm di spessore. Ciò è ottenuto facendo ruotare il substrato, al centro del quale era stata depositata una goccia di fotoresist, a una certa velocità, funzione della viscosità del fotoresist stesso. Le proprietà fisiche del fotoresist si modificano con l'esposizione alla luce. La selettività dell'esposizione viene determinata dalle maschere che sono poste tra la sorgente di radiazioni e il substrato. Tali maschere possono essere poste a contatto (fotolitografia per contatto) o molto vicine al fotoresist (fotolitografia per prossimità). Nella fotolitografia per contatto, le maschere vengono pressate sul wafer ricoperto precedentemente dal fotoresist. Questa operazione e il successivo distacco causano difetti sia sulla maschera stessa sia sul wafer e comportano la necessità della sostituzione periodica delle maschere. Inoltre, malgrado la pressatura delle maschere, il contatto può risultare non uniforme e dar luogo a variazioni di accostamento (anche di parecchi μm) che causano imperfezioni al circuito. Malgrado questi svantaggi, la fotolitografia per contatto è ancora largamente utilizzata per la sua alta risoluzione. La fotolitografia per prossimità si effettua ponendo le maschere a una distanza di circa 20÷50 μm. Questa tecnica, pur evitando gli svantaggi del contatto tra la maschera e il wafer, ha un potere di risoluzione inferiore. Le apparecchiature commerciali per la fotolitografia sono predisposte in modo da permettere la selezione del tipo di fotolitografia, per contatto o per prossimità, a seconda della risoluzione desiderata. In alternativa, la tecnica della fotolitografia elettronica, che utilizza un E-Beam, permette di realizzare direttamente la geometria desiderata sul wafer, evitando l'uso delle maschere; l'E-Beam permette infatti di impressionare direttamente il fotoresist sul wafer, ottenendo elevate risoluzioni. Ovviamente, dovendo l'E-Beam effettuare la scansione di tutta la superficie del wafer, il processo è lento e quindi adatto a realizzazioni di un numero limitato di circuiti (realizzazione di prototipi).

La deposizione. - È il procedimento chimico-fisico che permette di depositare vari tipi di materiali sul substrato, al fine di realizzare i dispositivi d'interesse. Gli spessori di deposizione sono in alcuni casi molto sottili (per es., lo strato di SiO₂ è di circa 200 Å), in altri più spessi (fino anche a 20 μm) e impiegano materiali isolanti, resistivi, dielettrici, semiconduttori drogati (questi ultimi utilizzati per una successiva diffusione all'interno del substrato), metalli. Le tecniche per la realizzazione della deposizione sono di due tipi: deposizione diretta e deposizione chimica. Con deposizione diretta si intende la deposizione del materiale per evaporazione o per bombardamento ionico (sputtering). L'evaporazione si realizza facendo evaporare il materiale da deporre sul substrato mediante il controllo dei parametri di pressione e temperatura all'interno di una camera di evaporazione. In questo modo il materiale viene deposto su tutta la fetta di silicio (e anche all'interno di tutta la camera di evaporazione). La tecnica di sputtering consiste nel bombardare con ioni ad alta energia il materiale da deporre, in modo da rimuovere le molecole del materiale che successivamente si depositeranno sul substrato. La deposizione chimica può essere realizzata in due modi: attraverso una reazione di due gas che diano luogo a un precipitato solido sulla superficie del substrato, oppure utilizzando un composto gassoso che, scaldandosi, libera le molecole del materiale che si intende depositare.

L'attacco. - È l'operazione che serve a rimuovere il materiale in eccedenza sulla superficie del substrato o a scavare opportunamente una certa geometria in un materiale depositato sul substrato stesso. Le aree che devono essere rimosse sono quelle che non sono protette dal fotoresist precedentemente impressionato tramite la mascheratura. Un processo di fabbricazione tipico prevede un gran numero di operazioni di attacco su diversi materiali, e avviene mediante l'uso di prodotti chimici in fase liquida che reagiscono con il materiale da rimuovere (attacco bagnato, wet etching) o attraverso un bombardamento ionico che lo rimuove meccanicamente, oppure attraverso l'uso di un plasma (attacco a secco, dry etching). La differenza tra i due metodi di attacco risiede nel fatto che l'attacco bagnato rimuove il materiale isotropicamente, e quindi lo rimuove anche sotto lo strato di protezione del fotoresist, mentre l'attacco a secco lo rimuove in una direzione preferenziale. È evidente che con l'attacco a secco possono essere realizzate geometrie a più alta risoluzione.

La diffusione. - È l'operazione che consente la migrazione forzata di impurità nel substrato o in altri materiali in modo controllato. Il profilo di diffusione, ovvero la concentrazione delle impurità in funzione della profondità del substrato, viene controllato attraverso la temperatura e il tempo di esposizione del substrato alla sorgente delle impurità. Possiamo distinguere due metodi per la realizzazione della diffusione delle impurità: diffusione in fase solida o gassosa, diffusione per impiantazione ionica. Nella diffusione in fase solida la sorgente delle impurità viene deposta sul substrato, mentre nella diffusione in fase gassosa il substrato viene esposto alle impurità. Nella diffusione per impiantazione ionica, invece, le impurità vengono accelerate e lanciate contro il substrato, andandosi a deporre sugli strati superficiali del reticolo cristallino. Successivamente, un opportuno trattamento termico consente di far diffondere le impurità all'interno del substrato, realizzando così il profilo di diffusione richiesto.

L'accrescimento epitassiale. - È il processo per realizzare la crescita di un materiale monocristallino su un substrato dello stesso materiale, o di materiale diverso, in modo da ottenere strati di diverse proprietà fisiche. Questo accrescimento viene eseguito esponendo il substrato a gas o vapori che, con opportune reazioni chimiche, depositano il materiale sulla superficie del substrato stesso. Il processo di crescita dev'essere sufficientemente lento per evitare fenomeni di disomogeneità o fratture nel cristallo. La crescita epitassiale viene anche utilizzata per realizzare lo stesso substrato.

L'ossidazione. - È il processo di crescita di ossidi sul substrato, utili soprattutto per ottenere strati isolanti. È realizzato mediante l'esposizione del substrato a gas contenenti molecole di ossigeno. Poiché il substrato è tipicamente silicio, il processo di ossidazione produce il diossido di silicio (SiO₂) che è un buon isolante. Infatti esso viene utilizzato per isolare strati conduttori diversi. Il processo di crescita dell'isolante provoca anche un 'consumo' del substrato di cui bisogna tenere conto.

La struttura di un transistore MOS consiste in due regioni fortemente drogate con impurità di tipo opposto a quelle con le quali è drogato il substrato, e di una zona intermedia, detta canale, che conserva invece le proprietà del substrato e forma quindi due giunzioni con le zone di diffusione adiacenti (i terminali source e drain). Le proprietà elettriche del canale sono condizionate dal campo elettrico prodotto da uno strato di polisilicio sovrastante, elettricamente isolato (il terminale gate).

Nel caso di transistori MOS a canale n, una tensione positiva applicata al gate di polisilicio muove gli elettroni presenti nel substrato verso l'interno del canale: quando la concentrazione di elettroni è sufficiente a bilanciare la barriera di potenziale che si forma alle giunzioni di source e drain, si ha conduzione attraverso il canale. Si ottiene in questo caso il cosiddetto MOS ad arricchimento (enhancement). Per ottenere elementi resistivi, la cui realizzazione diretta è molto difficile in tecnologia MOS, si utilizzano i transistori a svuotamento (depletion). In questi transistori, la zona del canale è riempita di elettroni nella fase costruttiva, di solito mediante l'impiantazione di atomi che hanno elettroni esterni in più rispetto agli atomi del substrato. In questo modo, il transistore è sempre in conduzione a meno che non venga applicata al gate una tensione negativa in grado di allontanare gli elettroni dalla zona del canale. Il resistore è ottenuto connettendo direttamente il gate al terminale source. Un funzionamento analogo si ha per i due tipi di transistori MOS a canale p.

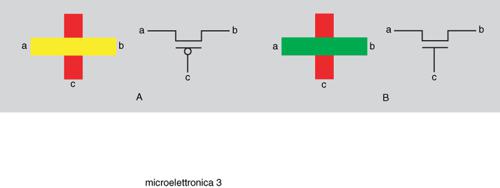

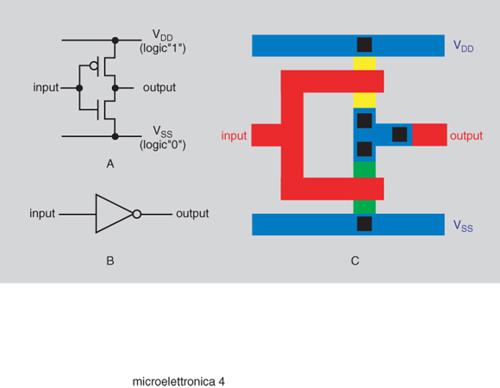

Nella tecnologia CMOS, nel substrato di tipo p o n vengono create, mediante diffusione, delle zone con drogaggio di nome opposto a quello del substrato, dette isole (well). La presenza di queste isole consente la realizzazione contemporanea di transistori MOS a canale p e a canale n. Nella tecnologia MOS e CMOS si realizzano quindi strutture a strati sovrapposti di tre tipi differenti: strati di diffusione, di polisilicio e metallici di alluminio. Tutti gli strati sono conduttori e quindi ciascuna delle piste che si realizza con uno qualunque degli strati è equivalente a un conduttore; pertanto, gli strati sono sempre isolati tra loro tranne che nei punti destinati al contatto. La tecnologia prevede che sia realizzato prima lo strato di ossido, poi lo strato di polisilicio, poi la diffusione e successivamente gli strati metallici. Quando è stato realizzato lo strato di polisilicio, esso viene mascherato e la parte non utile viene rimossa con attacco acido insieme con l'ossido sottostante. Poi, previa opportuna mascheratura, viene effettuata la diffusione: il polisilicio maschera così le zone a esso sottostanti. Se una pista di diffusione incrocia una pista di polisilicio si forma un transistore MOS. Infatti, nella zona sottostante al polisilicio si forma il canale e le due parti della striscia di diffusione formano il source e il drain del transistore. È chiaro che nella tecnologia CMOS servono due tipi di diffusione che vengono quindi eseguiti separatamente in passi successivi. Per ultimi vengono realizzati gli strati metallici, che sono ottenuti per deposizione e poi mascherati e attaccati. La progettazione del microcircuito consiste nella definizione della geometria dei vari strati (layout), a ciascuno dei quali viene assegnato un colore convenzionale nella presentazione su video (fig. 3). In particolare, tutti i dati del layout sono memorizzati in un insieme di dati numerici, aggiornato di continuo, man mano che la progettazione procede, dall'elaboratore videografico adibito al CAD. In fase realizzativa, l'insieme dei dati che definiscono il layout è elaborato da opportune macchine automatiche che producono le maschere necessarie per la realizzazione dei processi fotolitografici relativi ai singoli strati. In fig. 4 è mostrato il layout di un invertitore che rappresenta uno dei circuiti più semplici e realizza la funzione logica di negazione (se l'ingresso logico è 1 l'uscita logica è 0 e viceversa). Esso può essere considerato come una porta logica (logic gate) elementare.

Occorre notare che, in un processo in tecnologia CMOS, non sono realizzati solo i componenti fondamentali, e cioè i MOSFET a canale p e i MOSFET a canale n, ma anche altri componenti quali condensatori, resistori, diodi, BJT npn, BJT pnp. Tuttavia, essendo il processo CMOS ottimizzato per la realizzazione di transistori MOSFET, i transistori BJT e i diodi eventualmente realizzati presentano caratteristiche non ottimizzate e spesso sono addirittura considerati come componenti parassiti (non desiderati) per il progetto stesso.

Il processo tecnologico prevede che le maschere dei vari strati siano applicate successivamente alla struttura per ottenere la sua forma completa (fig. 5). Ciò implica che le successive maschere siano allineate in senso verticale con la parte di struttura già realizzata. Questo allineamento avviene sempre con un certo errore, tanto più piccolo quanto più le procedure sono state affinate. È necessario quindi che le dimensioni delle piste e dei transistori elementari siano ragionevolmente più grandi dell'errore commesso affinché esso influenzi poco le caratteristiche della struttura. Si indica con λ la larghezza minima che deve avere il canale di un MOS, affinché le caratteristiche del transistore stesso non siano influenzate in maniera apprezzabile dagli errori di allineamento: la quantità λ rappresenta una misura della precisione con la quale possono essere realizzate le strutture integrate. È evidente che la realizzazione di λ molto piccoli è altamente desiderabile. In primo luogo, una piccola larghezza di canale significa piccole dimensioni del singolo transistore e, perciò, piccole dimensioni dell'intera struttura, che può essere quindi più complessa a parità di dimensioni esterne; in secondo luogo, ma più importante, una piccola larghezza di canale significa anche piccole dimensioni del gate di polisilicio del transistore e quindi piccola capacità parassita del gate stesso. Di conseguenza, i tempi di salita dei segnali sono minori e i circuiti possono operare in tempi più brevi. Il tempo di salita è un parametro utile per la progettazione di circuiti analogici ed è legato alle costanti di tempo del circuito stesso. Nell'elettronica numerica i parametri significativi sono i tempi di ritardo td introdotti dall'attraversamento del segnale numerico nelle varie porte logiche. Attualmente si possono ottenere valori di λ dell'ordine di alcuni decimi di μm e valori di td dell'ordine di decine di picosecondi.

Uso dei mezzi di progettazione automatica (CAD)

Fino a qualche tempo fa la progettazione di microcircuiti si indirizzava verso la realizzazione di funzioni logiche anche complesse ma di uso generale. Questa progettazione si esauriva all'interno delle ditte costruttrici di circuiti integrati che costruivano in grande quantità i dispositivi che i progettisti di sistemi si limitavano poi a usare come dei semplici componenti. Il continuo progredire della tecnologia ha reso possibile la specializzazione e la personalizzazione dei microcircuiti verso le più disparate applicazioni e la costruzione di un intero sistema all'interno di un solo chip. Mentre la realizzazione tecnologica è diventata pressoché automatica, la progettazione e i mezzi CAD sono diventati sempre più complessi e differenziati, creando l'esigenza di una grande varietà di progettisti altamente specializzati. In effetti, la progettazione di chip molto complessi richiede un vasto spettro di competenze e quindi la ripartizione del lavoro tra più persone. Comunque, il tempo di sviluppo non può essere ridotto al di sotto di un tempo minimo aumentando il numero dei progettisti, ma solo perfezionando le procedure di progetto. Per questo motivo, la messa a punto di nuovi strumenti CAD è un campo di ricerca molto importante in m., nel quale operano molte università (soprattutto negli USA) e molte ditte, sia per uso interno che per commercializzazione dei relativi prodotti software. Le problematiche del CAD in m. riguardano un vasto spettro di problemi, in particolare: la descrizione funzionale del circuito, la sua simulazione logica, la generazione automatica del layout, l'estrazione dei parametri, la simulazione circuitale, la verifica delle regole di progetto e infine, per il collaudo del chip, la generazione di sequenze di ingresso significative (fig. 6).

La descrizione funzionale del circuito ne descrive il funzionamento a partire dalle sue specifiche e caratteristiche ad alto livello senza considerare il suo schema costitutivo. Esso viene descritto con una sintassi molto simile a quella di un linguaggio di programmazione, come fosse un listato di un programma. Un linguaggio molto utilizzato a tale scopo è il VHDL (Very high speed integrated circuit Hardware Description Language, linguaggio di descrizione hardware per circuiti integrati a elevatissima velocità). Inizialmente il circuito può essere descritto da un punto di vista funzionale senza alcun riferimento alla tecnologia che sarà utilizzata, e solo successivamente, con un grado di dettaglio via via crescente, può essere particolarizzato per un certo processo tecnologico. Il passaggio dalla descrizione funzionale allo schema circuitale avviene tramite un'operazione di sintesi logica realizzata con appositi programmi che sfruttano complessi algoritmi di ottimizzazione, controllati dal progettista mediante opportuni vincoli quali la minimizzazione dei tempi di ritardo totali o la limitazione delle porte logiche da utilizzare. La simulazione logica consente di verificare la correttezza del circuito ricavato dalla sintesi logica o dall'assemblaggio manuale delle celle elementari con le quali viene realizzata la struttura, che può crescere in relazione alla possibilità di controllare il funzionamento logico della parte già assemblata, rendendo pertanto possibile la connessione di nuove parti del sistema da integrare. La simulazione logica consente inoltre di studiare, in prima approssimazione, i ritardi di propagazione dei segnali, cosa questa che permette di sincronizzare nella maniera opportuna le diverse parti e di valutare, in prima istanza, le possibilità del circuito in termini di velocità di elaborazione. Questa valutazione è in generale di aiuto per stabilire se l'architettura scelta è idonea ad assicurare le richieste prestazioni.

Un passo fondamentale nel progetto di un chip consiste nella realizzazione del layout. Questo è interamente realizzato con mezzi CAD e presentato al progettista su di uno schermo (o anche su un grafico cartaceo) a colori. Quando il layout (o certe parti di esso) è completato, il comportamento elettrico della struttura è simulato circuitalmente, tenendo conto anche dei parametri parassiti (resistenze e capacità) introdotti dalle linee di connessione (nel caso di alte velocità operative, con frequenze maggiori di circa 40 MHz, è necessario considerare le connessioni come linee a costanti distribuite) e delle effettive prestazioni dei componenti attivi in condizioni operative. Questi componenti sono simulati a partire da modelli i cui parametri sono ricavati mediante misure effettuate sui componenti realizzati con la tecnologia in uso, e che variano quindi da una foundry all'altra. In particolare, simulazioni di questo tipo consentono di valutare i tempi di salita dei segnali e le loro velocità di propagazione. Ciò è particolarmente importante perché potrebbe accadere che segnali che dovrebbero essere presenti simultaneamente sulle porte di ingresso di una cella, arrivino in realtà distanziati nel tempo dando luogo, nel breve intervallo corrispondente al ritardo di uno dei segnali rispetto all'altro, a un comportamento anomalo della cella in esame. La simulazione circuitale fornisce una valutazione abbastanza aderente alla realtà della velocità di processamento dei segnali ottenibile. Quando tale simulazione ha dato esito positivo, il layout è pronto per essere trasformato nel dispositivo fisico. È necessario però, prima della costruzione, un nuovo passo in cui viene verificata la rispondenza del layout alle regole di progetto tipiche della tecnologia utilizzata (DRC, Design Rule Checking). Le regole di progetto derivano dall'ordine delle operazioni successive, attuate per la realizzazione del dispositivo fisico, e dalle tolleranze implicate nelle operazioni stesse.

Metodologie di progettazione

Alcuni microcircuiti sono appositamente progettati, fino al livello del semplice transistore, per una applicazione specifica. Questo tipo di progettazione capillare (custom o full custom) è molto onerosa ma consente di ottimizzare le prestazioni della struttura da realizzare da tutti i punti di vista di interesse. Questi punti di vista possono essere, per es., la compattazione di un sistema complesso all'interno di un solo chip, o il raggiungimento di una velocità maggiore, rispetto a quella di un circuito d'uso generale, nell'esecuzione di certe operazioni, o semplicemente la possibilità di porre un sistema originale in una forma di hardware che sia molto difficile analizzare e imitare. Tuttavia, la progettazione custom viene affrontata solo nelle grandi industrie, che hanno un vasto mercato o costruiscono oggetti ad alto valore aggiunto e possono quindi recuperare gli ingenti costi di progettazione di queste strutture. Nel caso delle piccole industrie, che operano in campi particolari, è preferito l'uso di circuiti predisposti per molteplici applicazioni. Per es., nel campo dei dispositivi per il processamento del segnale, le piccole industrie preferiscono usare processori microprogrammabili piuttosto che processori dedicati, che avrebbero pure i loro vantaggi. Una serie di ragioni consigliano questo tipo di scelta: il microprogramma del processore di tipo generale può essere cambiato in qualsiasi momento, mentre invece un chip dedicato dev'essere riprogettato, ripetendo la procedura di fabbricazione anche per le modifiche più lievi; processori di tipo generale possono essere acquistati in pochi esemplari, mentre un chip dedicato dev'essere necessariamente realizzato in molti esemplari per ridurne il costo; il progettista addetto allo sviluppo del microprogramma può essere più facilmente reperito rispetto al progettista del microcircuito. In conclusione, il progetto di un chip full custom rappresenta un forte investimento che si possono permettere solo grandi industrie.

Un tipo di tecnologia a basso costo, e comunque apprezzabile rispetto alla soluzione con circuiti di tipo generale, consiste in microcircuiti precostruiti contenenti un determinato numero di componenti complessi di base (gate arrays). Tali componenti di base possono essere, per esempio, shift register, multiplexer, contatori o un certo numero di porte logiche. In tutti questi casi, il progettista si limita a connettere tra loro in maniera opportuna i componenti di base che, tra tutti quelli disponibili, realizzano la struttura voluta. Anche la fase di realizzazione tecnologica dei gate arrays è semplice e non particolarmente onerosa. D'altra parte, la struttura base è prodotta in molti esemplari per utenti diversi ed è quindi venduta a prezzi vantaggiosi. Tuttavia questo tipo di realizzazione si presenta attualmente in alternativa all'uso dei dispositivi logici programmabili (PLD, Programmable Logic Devices), che appaiono essere in crescente affermazione e risultano essere molto competitivi sulle medie quantità.

La tecnologia delle celle standard (standard cells) consiste nell'uso di celle elementari progettate, a livello di circuito e di layout, dalla stessa foundry che deve successivamente realizzare il progetto completo. Le celle elementari sono memorizzate su file e il progettista realizza il proprio chip costruendo un'architettura personalizzata costituita da queste celle base. Le possibilità offerte dal CAD consentono di sostituire automaticamente alle celle logiche elementari il loro layout disegnato secondo regole modulari utili per l'assemblaggio automatico. Intere parti logiche del sistema sono frequentemente realizzate con la metodologia delle celle standard, dando luogo alle cosiddette macrocelle. Per le parti più importanti nell'assemblaggio di un sistema logico, quali PLA (Programmable Logic Array), ROM (Read Only Memory), RAM (Random Access Memory), sommatori, moltiplicatori, divisori ecc., si dispone in genere di programmi dedicati alla generazione automatica del layout, che producono a loro volta delle macrocelle. Il problema principale, in tale tecnologia, consiste nel posizionare (placement) nella maniera più opportuna le macrocelle sul layout della struttura completa. La ricerca della soluzione ottima di questo problema richiede una complessa gestione di tutti i collegamenti elettrici che uniscono le macrocelle fra di loro (routing). Come ottima può essere considerata la soluzione in cui l'area complessiva occupata dalla struttura completa è resa minima, oppure quella in cui è minimizzata la lunghezza massima delle connessioni. Con la tecnologia delle standard cells si ottiene un certo risparmio sui tempi e sui costi di progettazione rispetto alla tecnologia full custom; la fase di realizzazione tecnologica è in pratica la stessa. Ne segue che, dal punto di vista dei costi, la realizzazione del circuito è più onerosa rispetto al caso dei gate arrays, ma ha il vantaggio di inserire nel chip solo i circuiti che sono realmente utili (nel caso dei gate arrays, parte delle strutture disponibili sul chip non è utilizzata). Questo fatto consente un risparmio di area di silicio, ma il vantaggio maggiore consiste nel poter ridurre, rispetto ai gate arrays, le lunghezze dei collegamenti, dato che le celle possono essere disposte opportunamente, con un conseguente incremento della velocità operativa del chip. I vantaggi sono molto simili a quelli dei full customs.

Metodologie di collaudo

La m. ha consentito di minimizzare i problemi derivanti dai possibili guasti. Infatti, il microcircuito si presenta in generale di struttura molto robusta dal punto di vista meccanico, ed essendo monolitico non richiede interventi interni per il montaggio. Tuttavia, in fase di realizzazione tecnologica, vi sono molte cause che possono portare al non funzionamento di un microcircuito: impurezze nell'ambiente di lavorazione, errori nel posizionamento delle maschere ecc. In generale il rapporto fra il numero dei circuiti funzionanti rispetto al numero totale dei circuiti costruiti è chiamato resa del processo (yield) e tende ad aumentare con l'affinamento della tecnologia, in particolare con le condizioni degli ambienti in cui le operazioni sono svolte. Quest'ultimo è uno degli aspetti più difficili da ottimizzare, ma è essenziale poiché può condizionare tutto il processo produttivo. Se la resa è troppo bassa tutto il processo dev'essere rivisto, in quanto una percentuale troppo alta di circuiti dev'essere scartata. Per selezionare i circuiti validi da quelli non funzionanti si usano complesse procedure di collaudo (testing) sui singoli circuiti costruiti, utilizzando particolari macchine che effettuano tali operazioni con la massima velocità e precisione, dette ATE (Automated Testing Equipment, apparati di testing automatico). La certezza del corretto funzionamento del circuito si ottiene verificando, per tutti i possibili ingressi, la correttezza delle uscite. Poiché un tale modo di procedere può richiedere tempi di impegno eccessivamente lunghi per le macchine di testing, il collaudo viene effettuato con metodi che massimizzano il rapporto tra la percentuale di cause di guasto verificate e il tempo richiesto. A tal fine si è affermata la tendenza a considerare i problemi del testing già in fase di progetto (design for testability), scegliendo architetture più facilmente collaudabili, ovvero predisponendo la possibilità di verifica sia a livello circuitale, attraverso appositi circuiti all'interno del chip stesso (BIST, Bult-In Self Test) che effettuano una sequenza di testing producendo delle uscite che indicano la presenza di malfunzionamenti, sia a livello software, definendo sequenze di ingresso adatte a dare la maggiore copertura di possibili cause di guasto. Inoltre, tenendo conto della grande complessità dei microcircuiti realizzabili in VLSI, possono essere costruite architetture in grado di funzionare anche in presenza di uno o più guasti circuitali (fault-tolerant); tali circuiti, basati su un certo grado di ridondanza strutturale, possono essere anche capaci di autodiagnosticare il guasto e di riconfigurarsi in maniera da non utilizzare la parte guasta, mantenendo il corretto funzionamento.

bibliografia

A.S. Sedra, K.C. Smith, Microelectronic circuits, New York 1982, 1998⁴.

N.H.E. Weste, K. Eshraghian, Principles of CMOS VLSI design. A system perspective, Reading (Mass.) 1985, 1993².

K.R. Laker, W.M.C. Sansen, Design of analog integrated circuits and systems, New York 1994.

ULSI technology, ed. C.Y. Chang, New York 1996.

R.C. Jaeger, Microelectronic circuit design, New York 1997.

Modern semiconductor device physics, ed. S.M. Sze, New York 1998.

A. Schenk, Advanced physical models for silicon device simulation, New York 1998.

Th.L. Floyd, D. Buchla, Fundamentals of analog circuits, Upper Saddle River (N.J.) 1999.

Future trends in microelectronics, ed. S. Luryi, J. Xu, A. Zaslavsky, New York 1999.

J.H. Lau, S.-W.R. Lee, Chip scale package, CSP. Design, materials, processes and applications, New York 1999.