ELETTRONICA

Elettronica

Le tecnologie microelettroniche si sono contraddistinte nel tempo per un processo di miniaturizzazione delle dimensioni fisiche dei dispositivi elementari, che ha consentito di elevarne in modo considerevole le prestazioni e di permettere un incremento esponenziale della scala di integrazione dei circuiti a parità dei costi di produzione, che si sono mantenuti proporzionali all'estensione della superficie di silicio impegnata. Le dimensioni caratteristiche dei dispositivi avanzati variano fra 90 e 65 nm, mentre il numero di transistori integrabili su singolo chip si colloca ben al di sopra di un miliardo. Si ritiene che questo processo di contrazione delle dimensioni possa continuare almeno sino all'anno 2015, quando raggiungeranno valori dell'ordine di 20÷25 nm.

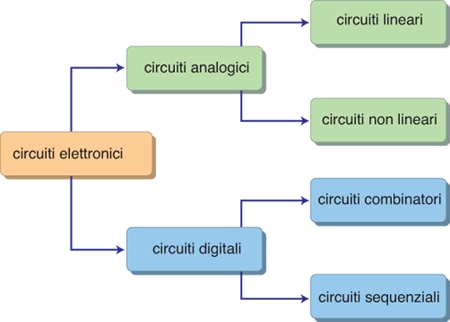

I circuiti elettronici possono essere suddivisi in due grandi classi funzionalmente distinte: quella dei circuiti analogici e quella dei circuiti digitali. I primi si caratterizzano per il fatto di generare, elaborare e trasmettere segnali variabili con continuità nel tempo. Per la natura dei circuiti e dei dispositivi che li compongono, tali segnali sono generalmente rappresentati da tensioni o da correnti elettriche. I circuiti digitali sono viceversa idonei a rappresentare segnali suscettibili di assumere un numero discreto di stati logici che, nella maggior parte dei casi, è semplicemente uguale a due, il bit, a cui sono convenzionalmente associati i valori 0 e 1.

I circuiti analogici possono essere classificati come lineari o non lineari. I primi eseguono funzioni lineari, come l'amplificazione, l'integrazione e il filtraggio, i secondi eseguono funzioni che coinvolgono operazioni non lineari, come la generazione di oscillazioni, la modulazione di ampiezza e la conversione di frequenza.

I circuiti digitali possono essere di tipo combinatorio o sequenziale. I circuiti combinatori sono caratterizzati dal fatto che il segnale di uscita dipende esclusivamente dal valore degli ingressi al tempo considerato, oltre che dalla natura del circuito. Esempi tipici di circuiti combinatori sono le porte logiche che realizzano le funzioni booleane elementari, come il NOT, il NAND e il NOR. Lo stato di un circuito sequenziale, viceversa, dipende non soltanto dal valore degli ingressi al tempo presente, ma anche dalla successione dei valori assunti dagli ingressi nel passato. Pertanto, un circuito sequenziale è dotato di memoria. Esempi di circuiti sequenziali sono, per l'appunto, le memorie, i registri e le macchine a stati finiti. La fig. 1 fornisce una rappresentazione visiva della classificazione dei circuiti.

La motivazione per la quale si fa uso di circuiti elettronici digitali, anche se il contenuto informativo di un segnale analogico è molto più elevato, è dovuta al fatto che nel processo di elaborazione di segnali analogici si introducono inevitabilmente rumore e distorsione. Viceversa, un segnale digitale, anche se degradato, deve essere semplicemente riconosciuto come uno 0 o come un 1 e, eventualmente, ripristinato al suo livello basso o alto. Inoltre, facendo uso di un numero sufficientemente elevato di bit, è possibile rappresentare il valore di una grandezza fisica con precisione grande a piacere.

La tecnologia realizzativa è influenzata da prestazioni (velocità, consumo di potenza e, per i circuiti analogici, rapporto segnale-rumore, dinamica) e costo. Per le applicazioni digitali la tecnologia dominante è quella che si avvale di transistori a effetto di campo metallo-ossido-semiconduttore (CMOS, Complementary Metal Oxide Semiconductor) a canale n e a canale p realizzati in silicio. Per le applicazioni analogiche la tecnologia di riferimento è quella bipolare o, più frequentemente, BiCMOS, che rende disponibili in un unico circuito integrato sia dispositivi CMOS sia bipolari. La ragione per cui i transistori bipolari (BJT) sono tuttora preferiti per le applicazioni analogiche ad alte prestazioni è dovuta alla loro più elevata capacità di erogazione di corrente, che si presta per la realizzazione di stadi di potenza, e alla loro più contenuta rumorosità in bassa frequenza rispetto ai MOSFET (Metal Oxide Semiconductor Field Effect Transistor).

Circuiti analogici

Per seguire l'evoluzione dell'e. analogica nel corso degli anni è sufficiente osservare gli schemi elettronici degli amplificatori operazionali (op-amp) e degli amplificatori lineari di potenza. Le prestazioni globali di un op-amp sono dipendenti da quelle di ogni singola sua parte. Ognuna di esse viene ottimizzata consentendo infine di ottenere un sistema in un singolo chip in grado di soddisfare le esigenze sempre crescenti dei progettisti di circuiti analogici. Questi richiedono op-amp a basso consumo, con limitato off-set di ingresso e di uscita, basso rumore in ampi intervalli di frequenza, bassa tensione di alimentazione, forte reiezione a eventuali variazioni della tensione di alimentazione, correnti di bias di ingresso sempre più piccole, elevati guadagni a catena aperta, elevata velocità di variazione (slew rate), elevata corrente di uscita, e così via. Gli op-amp, amplificatori a elevato guadagno e in grado di amplificare segnali continui oltreché alternati, sono stati concepiti inizialmente per eseguire operazioni lineari tipo somma, sottrazione, derivazione e integrazione e per risolvere equazioni differenziali. Essi vengono impiegati nel campo della preamplificazione di piccoli segnali anche in presenza di tensioni indesiderate: in questo caso gli op-amp sono detti per strumentazione e sono caratterizzati da prestazioni eccezionali. Per ottenere op-amp di particolari prestazioni sono necessari procedimenti tecnologici sempre più accurati, segmenti di processo molto precisi e materiali di qualità sempre migliore, ossia fette di silicio con un numero minimo di difetti e tecniche di ossidazione, impiantazione ionica, deposizione di materiali e di etching di grande riproducibilità. Sono tuttavia altrettanto importanti soluzioni circuitali innovative e accorgimenti intelligenti che possano consentire di conferire al componente finale le caratteristiche desiderate. Un op-amp può essere considerato come un complesso circuito elettronico formato dai seguenti blocchi fondamentali: un amplificatore differenziale di ingresso in grado di amplificare i segnali differenza e attenuare quanto più possibile i segnali di modo comune, una serie di amplificatori intermedi, un integratore e uno stadio di uscita possibilmente a bassa impedenza. Tutta la struttura deve poi essere messa a operare in un punto di lavoro particolare tramite generatori di corrente stabili nel tempo e indipendenti da variazioni di temperatura in un intervallo che può variare da 0 °C a 100 °C per op-amp di tipo standard o da −30 °C fino a 120 °C per op-amp da impiegare per particolari prestazioni. Per applicazioni spaziali, per es., dove gli errori devono essere ridotti al minimo, la scelta dei componenti ha un ruolo determinante e gli op-amp vengono selezionati e addirittura pretrattati termicamente. I generatori di corrente continua impiegati per la polarizzazione degli elementi attivi di un op-amp sono detti circuiti specchi di corrente e possono essere di tipo semplice o multipli. Negli ultimi anni i generatori di corrente stabili nei confronti delle variazioni di temperatura sono entrati in una moltitudine di circuiti funzionali: convertitori analogico-digitali, interfacce per la misura delle proprietà dei sensori impiegati per la rivelazione di grandezze fisiche, chimiche e biologiche, generatori di segnali lineari e non lineari del tempo per applicazioni nel campo delle misure ottiche, e così via.

Gli specchi di correnti (current mirror, CM) hanno la caratteristica rilevante di fornire una corrente poco dipendente dalla temperatura. Non sono generatori di corrente ideali, nel senso che non hanno resistenze elevatissime di uscita, ma per valori delle resistenze di carico non troppo elevati presentano l'unica caratteristica di generare tali correnti poco sensibili alla temperatura negli intervalli standard di impiego. Esistono specchi di corrente realizzati con transistori bipolari di tipo p e di tipo n e altri realizzati con strutture tipo MOSFET a canale n e a canale p.

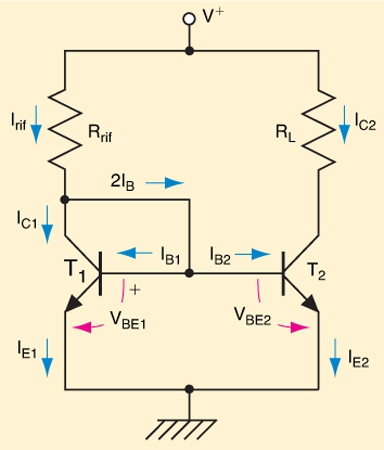

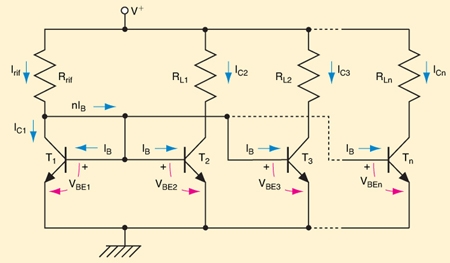

La fig. 2 mostra un CM formato da una coppia di transistori di tipo n. Il primo transistore presenta il collettore collegato con la base e questa configurazione non consente al dispositivo attivo di amplificare, mentre conferisce al medesimo la peculiarità unica secondo la quale la dipendenza della corrente di collettore dalla temperatura è minima. Il secondo transistore può amplificare, ma considerato da solo non avrebbe la peculiarità di dipendenza termica della propria corrente di collettore, di cui gode, invece, il primo. Il collegamento diretto delle due basi fa sì che le due tensioni base emettitore dei due transistori siano topologicamente uguali; ciò dà luogo, se i transistori sono identici, a correnti di collettore uguali. Nel secondo transistore circola pertanto una corrente di collettore pari a quella circolante nel primo, da cui consegue il nome. Resta da verificare se il secondo transistore, pur generando una corrente di collettore pari a quella del primo, riesce a sostenere la propria corrente di collettore dotata della proprietà di poca dipendenza termica che invece caratterizza pienamente il primo transistore. Il risultato di una semplice indagine analitica mostrerebbe che il CM è in grado di specchiare una corrente di collettore che non potrà mai avere la trascurabile dipendenza termica tipica della prima parte del CM considerata isolata, ma sarà in grado di generare una corrente la cui stabilità termica viene peggiorata solamente di un fattore due. Dovendo impiegare più rami di generatori di corrente termicamente stabili si può ricorrere all'uso di CM multipli (fig. 3), tenendo però presente che ogni ramo aggiuntivo introduce un peggioramento delle prestazioni.

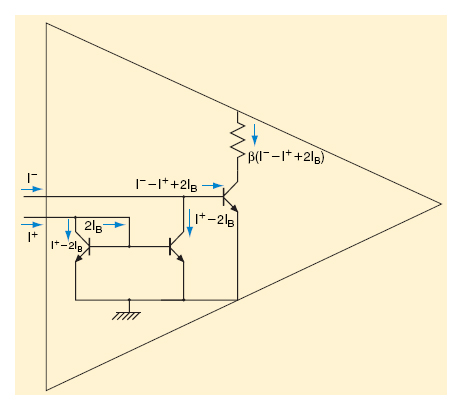

Amplificatori operazionali di Norton

Un'altra applicazione degli specchi di corrente è il loro uso nello stadio d'ingresso di un amplificatore operazionale di tipo Norton (fig. 4; nella figura è mostrato solamente il circuito di ingresso perché riguarda, appunto, un'applicazione particolare dei CM; viene sottinteso che la parte non indicata, per semplicità, all'interno del triangolo rappresenta un op-amp standard, ossia un amplificatore di tensione). Un amplificatore così progettato è in grado di operare su una differenza di correnti in ingresso invece che di tensioni. In questo caso, infatti, in virtù della presenza di uno specchio di corrente in ingresso dell'op-amp è possibile generare una corrente pari a circa (I−−I+), se si trascura un piccolo errore dato dal doppio della corrente di base IB, normalmente di entità trascurabile se il progetto è stato ben curato a livello tecnologico. L'uscita dell'op-amp di Norton è ancora una tensione a bassa impedenza del tipo che si ha negli op-amp standard, dove l'uscita risulta essere proporzionale alla differenza delle tensioni in ingresso. In conclusione, i CM si rivelano ottimi generatori di corrente se la quasi totale indipendenza dalla temperatura è la caratteristica più importante da considerare.

Logiche combinatorie e sequenziali

Per un corretto funzionamento dei circuiti logici a elevata complessità, le tecnologie con le quali vengono realizzate le funzioni logiche elementari devono soddisfare un certo numero di requisiti funzionali: elevati margini di immunità ai disturbi; capacità di pilotaggio di un numero elevato di porte logiche connesse in cascata (fan out); disaccoppiamento ingresso-uscita; compatibilità dei livelli logici di ingresso e di uscita.

Il primo requisito è motivato dall'esigenza di ripristinare i livelli logici anche in presenza di rumore termico, o di disturbi di varia natura che ne alterino l'integrità; poiché i circuiti logici sono tipicamente caratterizzati da lunghe catene di porte logiche connesse in cascata, è necessario che, a fronte di una fluttuazione del segnale di ingresso a una porta logica, non si produca una corrispondente variazione della tensione di uscita. Il secondo requisito richiede che una porta logica debba essere in grado di pilotarne due o più connesse in cascata alla prima, mantenendo l'integrità dei livelli di tensione; ciò implica che la resistenza di ingresso della porta logica sia molto maggiore della sua resistenza di uscita, e che la stessa sia dotata della capacità di amplificazione di potenza. La proprietà di disaccoppiamento ingresso-uscita richiede che, anche se l'uscita di una porta logica è ovviamente determinata dallo stato degli ingressi, il valore della tensione di uscita non influenzi alcuno dei livelli di ingresso; ciò implica che i dispositivi che compongono la porta logica siano caratterizzati da un elevato livello di isolamento fra i terminali di ingresso e di uscita. La compatibilità dei livelli logici di ingresso e di uscita è un requisito che si rende necessario per consentire la connessione diretta di due o più porte logiche senza fare uso di circuiti di interfaccia per l'adattamento dei livelli di tensione e di corrente.

Porte logiche elementari in tecnologia CMOS

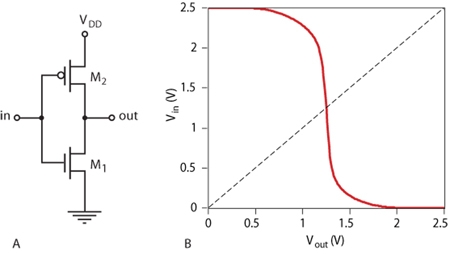

Il circuito che realizza la funzione NOT, detto invertitore, può essere implementato in tecnologia CMOS con due soli transistori, uno a canale n e uno a canale p, opportunamente connessi, come rappresentato in fig. 5 A. In particolare, i gates dei due MOSFET sono cortocircuitati e formano il terminale di ingresso dell'invertitore; i sources dei due transistori n e p sono connessi rispettivamente a massa e alla tensione di alimentazione positiva VDD, mentre i due drains sono cortocircuitati e formano il nodo di uscita dell'invertitore. Si riconosce come tale circuito possa essere riguardato come un amplificatore a source comune avente struttura complementare.

Si definisce tensione di soglia VTN di un MOSFET a canale n il valore limite della tensione gate-source VGS che determina la transizione fra lo stato di interdizione e quello di conduzione del transistore. Più precisamente, se è verificata la relazione VGS〈VTN, il transistore è spento, mentre, nel caso opposto, è acceso. Il transistore è progettato in modo che VTN∿VDD/5. In maniera analoga si definisce la tensione di soglia VTP di un MOSFET a canale p. Per questo transistore, tuttavia, la tensione di soglia è negativa e circa uguale in modulo a VTN; inoltre esso si accende quando la tensione VGS è negativa e minore della tensione di soglia VTP. Si definisce, infine, soglia logica dell'invertitore il valore VLT per il quale le tensioni di ingresso e di uscita assumono lo stesso valore, ossia VI=VO=VLT. Nella condizione di soglia logica, l'invertitore è polarizzato nel punto di massimo guadagno differenziale di tensione, che assume tipicamente valori dell'ordine di svariate decine.

Il funzionamento come invertitore richiede viceversa grandi variazioni della tensione di ingresso, che sono necessarie per far emergere le non linearità della caratteristica ingresso-uscita. Quando i valori della tensione di ingresso VI sono compresi fra 0 e VTN, il transistore a canale n è spento in quanto VGS〈VTN, mentre il transistore a canale p è acceso perché VGS〈VTP.

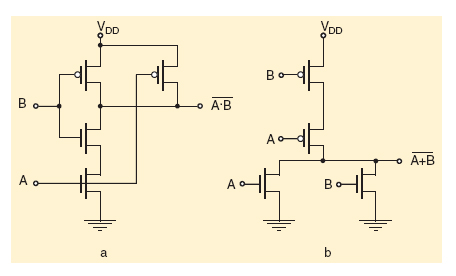

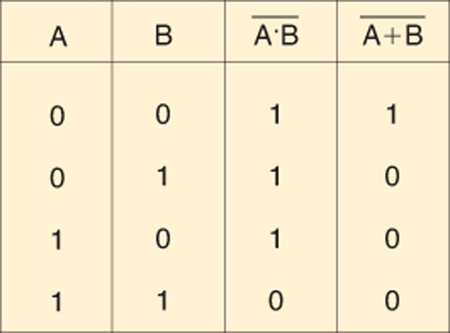

Pertanto, la tensione di uscita VO si porta a VDD. Analogamente, quando VDD+VTP〈VI〈VDD, il transistore a canale n è acceso mentre il transistore a canale p è spento, e la tensione di uscita si porta a massa. Per le suddette proprietà, il MOSFET a canale n si dice transistore di pull-down, mentre il MOSFET a canale p si dice transistore di pull-up. Associando il valore logico 0 alla tensione bassa e il valore 1 alla tensione alta, si riconosce che il circuito di fig. 5 realizza la funzione NOT. Se, partendo dalla condizione VI=0, si fa aumentare gradualmente la tensione di ingresso, la tensione di uscita varierà gradualmente da VDD a 0, come indicato in fig. 5 B. La porta NAND a due ingressi si realizza in tecnologia CMOS come indicato in fig. 6 a. La rete di pull-down si compone di due transistori a canale n connessi in serie, mentre la rete di pull-up si compone di due transistori a canale p connessi in parallelo. I gates dei transistori n e p sono connessi a due a due per formare i terminali di ingresso. Il nodo comune ai drains dei due transistori p e del secondo transistore n forma il terminale di uscita. Solo quando entrambi gli ingressi sono al livello logico alto esiste un canale conduttivo fra la massa e il nodo di uscita, mentre non si ha connessione fra uscita e VDD in quanto i transistori a canale p sono entrambi spenti. In tale condizione la tensione di uscita è 0. In tutte le altre configurazioni delle tensioni di ingresso, almeno un transistore p è acceso e almeno un transistore n è spento. Pertanto, l'uscita è alla tensione VDD. Questa modalità di funzionamento corrisponde alla funzione logica NAND (A ∙ B) descritta in fig. 7.

La porta NOR a due ingressi si realizza in tecnologia CMOS come indicato in fig. 6 b. La rete di pull-down si compone di due transistori a canale n connessi in parallelo, mentre la rete di pull-up si compone di due transistori a canale p connessi in serie. Solo quando entrambi gli ingressi sono al livello logico basso esiste un canale conduttivo fra VDD e il nodo di uscita, mentre non si ha connessione fra uscita e massa in quanto i transistori a canale n sono entrambi spenti. In tale condizione la tensione di uscita è VDD. In tutte le altre configurazioni delle tensioni di ingresso, almeno un transistore n è acceso e almeno un transistore p è spento. Pertanto, l'uscita è alla tensione 0. Questa modalità di funzionamento corrisponde alla funzione logica NOR (A + B) descritta in fig. 7.

L'esame della caratteristica ingresso-uscita di fig. 5 B rende possibili le seguenti considerazioni: l'elevato guadagno di tensione nella regione centrale della caratteristica rende possibile un elevato margine di immunità ai disturbi; la resistenza di ingresso dei transistori MOS è virtualmente infinita e, come tale, molto maggiore della resistenza di uscita, che è dell'ordine delle decine o centinaia di κ Ω, a seconda della loro polarizzazione, e ciò assicura un elevato fan out che, in questo caso, è limitato soltanto dal maggior ritardo di propagazione; l'isolamento dielettrico del gate comporta che, in condizioni stazionarie, le tensioni di ingresso della porta logica non siano influenzate dalla tensione di uscita, da cui discende il requisito di disaccoppiamento; i livelli logici basso e alto sono dati dalla tensione di massa e dalla tensione di alimentazione sia all'ingresso sia all'uscita, per cui tali livelli non sono influenzati dalle caratteristiche dei transistori, ed è così assicurata la compatibilità fra i livelli logici di ingresso e di uscita.

La struttura delle porte logiche NAND e NOR, che sono costituite da una rete di pull-down formata da transistori a canale n e da una rete complementare di pull-up formata da transistori a canale p, può essere generalizzata per la realizzazione di funzioni logiche arbitrariamente complesse. La complementarietà delle due reti deve assicurare che, se con una certa configurazione degli ingressi esiste un cammino conduttivo dal nodo di uscita a massa, non esista un analogo cammino dal nodo di uscita a VDD e, per converso, che l'esistenza di un cammino conduttivo dal nodo di uscita a VDD escluda la presenza di un tale cammino verso massa. Questa condizione rende verificata la proprietà di assenza di dissipazione per la porta logica CMOS in condizioni statiche, e garantisce che le tensioni corrispondenti ai due livelli logici siano esattamente 0 e VDD.

Prestazioni delle porte logiche CMOS

Le prestazioni delle porte logiche CMOS sono descritte principalmente da due parametri: il ritardo di propagazione e l'energia dissipata in un processo completo di commutazione. Il ritardo di propagazione tpd è definito come la media aritmetica fra il tempo di discesa tf e il tempo di salita tr della tensione di uscita, in risposta a una commutazione pressoché istantanea dell'ingresso. Indicando con CL la capacità totale di carico dell'invertitore e con INON e IPON le correnti di saturazione dei transistori di pull-down e di pull-up, rispettivamente, l'espressione del tempo di discesa è tf=(CLVDD/INON) mentre quella del tempo di salita è tr=(CLVDD/IPON). Il ritardo di propagazione è tanto più contenuto quanto minore risulta essere la capacità di carico e quanto maggiore è la capacità di erogazione di corrente dei transistori a canale n e a canale p.

Per quanto riguarda il consumo di potenza, con semplici considerazioni è possibile verificare che le porte logiche CMOS non dissipano potenza statica in condizioni stazionarie, in quanto la rete di pull-down o di pull-up sono sempre interdette e non esiste mai un cammino conduttivo per la corrente da VDD a massa.

L'energia ED complessivamente dissipata in un processo completo di commutazione vale CLVDD2. Questo semplice risultato compendia la prestazione di una tecnologia per quanto concerne il consumo di potenza di un microprocessore o, in generale, di un sistema di calcolo di architettura assegnata, in quanto l'esecuzione di un'istruzione, o di un qualsivoglia algoritmo, prevede un certo numero di commutazioni, e la potenza dissipata sarà un multiplo di CLVDD2.

Questa unità di energia dipende da due soli fattori: la capacità di carico CL e la tensione di alimentazione VDD. In linea di principio, la capacità di carico può essere ridotta attraverso un processo di miniaturizzazione dei circuiti, la qual cosa presuppone non solo una riduzione delle dimensioni fisiche dei transistori, ma anche delle piste di interconnessione e dei relativi contatti, che sono i massimi responsabili dell'occupazione di area di un circuito integrato. La tensione di alimentazione VDD può essere ridotta solo a prezzo di un peggioramento del ritardo di propagazione tpd, in quanto la corrente di saturazione decresce con legge superlineare al diminuire della tensione applicata, e tende da ultimo a un decremento esponenziale quando la tensione di alimentazione diviene comparabile o minore della tensione di soglia dei transistori.

Circuiti sequenziali in tecnologia CMOS

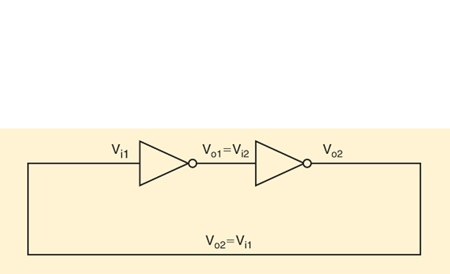

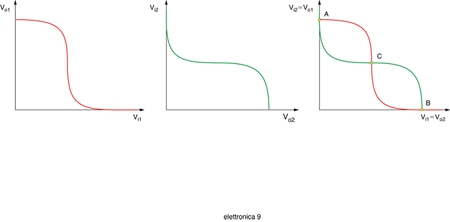

La più semplice rete logica sequenziale si ottiene connettendo in retroazione due invertitori CMOS, come mostrato in fig. 8. Indicando con I1 e I2 i due invertitori, si riconosce come l'uscita di I1 sia connessa all'ingresso di I2 e, analogamente, l'uscita di I2 sia connessa all'ingresso di I1. Se i due invertitori sono uguali e hanno pertanto la stessa soglia logica VLT, si comprende come un punto di equilibrio sia dato dalla condizione V01=V02=VLT. Il circuito possiede tuttavia due ulteriori punti di equilibrio, nei quali risulta V01=0, V02=VDD e inoltre V01=VDD, V02=0. L'esistenza di tre punti di equilibrio è illustrata visivamente dal diagramma di fig. 9, che rappresenta sul piano (V01, V02) le caratteristiche ingresso-uscita dei due invertitori. I tre punti di intersezione delle caratteristiche A, B, C rappresentano con tutta evidenza le possibili soluzioni del sistema di equazioni che governa il funzionamento del circuito, ossia i suoi punti di equilibrio.

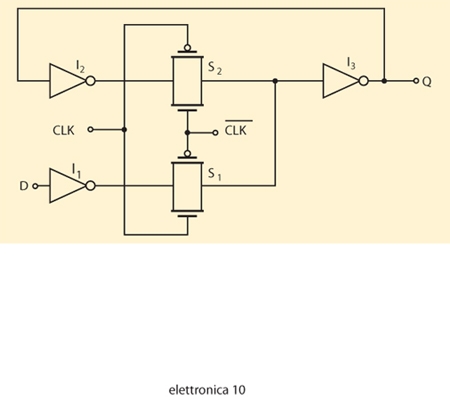

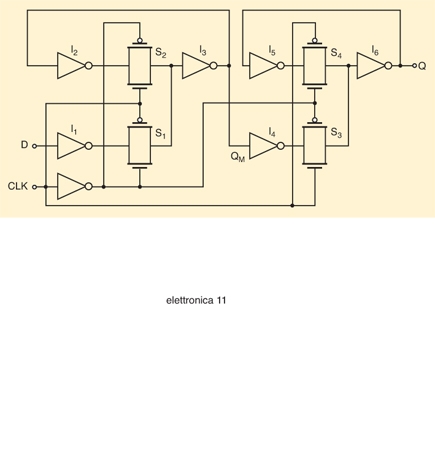

La teoria dei circuiti in retroazione ci dice inoltre che la condizione nella quale i due invertitori sono polarizzati sulla soglia logica (punto C) è un punto di equilibrio instabile, in quanto il guadagno di anello A1A2 è positivo e maggiore di 1. Viceversa, i due punti A e B in cui le tensioni di uscita sono 0 e VDD rappresentano due punti di equilibrio stabile, in quanto il guadagno di anello A1A2≪1. Pertanto, il circuito di fig. 8, denominato multivibratore bistabile, può essere polarizzato soltanto in uno di due stati stabili, in corrispondenza al quale risulterà V01=0, V02=VDD oppure V01=VDD, V02=0. Come tale, esso può essere utilizzato per memorizzare staticamente un bit di informazione e rappresenta quindi il nucleo di una cella di memoria statica.Si consideri ora la rete di fig. 10, composta da tre invertitori e due interruttori CMOS. I due interruttori comprendono un transistore a canale n e un transistore a canale p con source e drain interconnessi. Ai gates dei due transistori sono applicate due tensioni di clock in controfase ϕ e ϕ', in modo che i due transistori siano simultaneamente accesi oppure simultaneamente spenti. Quando la fase ϕ=1, l'interruttore S1 è acceso e il dato D accede all'ingresso dell'invertitore I2 situato sul cammino diretto del segnale. Esso comparirà pertanto in forma negata all'uscita (P=D'); in questa fase il circuito è trasparente al segnale di ingresso. Quando ϕ=0, viceversa, S1 si apre interdicendo il percorso del segnale, mentre S2 si chiude, connettendo I2 e I3 in retroazione positiva. Il circuito si polarizza pertanto in uno dei suoi stati stabili e mantiene la configurazione precedente con Q=D; in questa fase il circuito memorizza il dato D. Il circuito illustrato è detto latch e, quando opera in associazione con un altro latch pilotato in controfase, forma un registro statico, come illustrato in fig. 11. Nella configurazione di figura, il latch a monte si chiama master e quello a valle si chiama slave, a indicare che il primo comanda il funzionamento del secondo.

Latch e registri sono ampiamente utilizzati nei sistemi digitali per esigenze di sincronizzazione dei segnali. Infatti, quando i percorsi attraverso i quali sono generati due segnali di ingresso a una stessa porta logica sono molto diversi, il ritardo associato alla loro generazione può creare malfunzionamenti. L'uso di latch e registri serve pertanto a bloccare la propagazione incontrollata dei segnali attraverso una successione di porte logiche, e rende possibile la sincronizzazione di segnali che devono essere elaborati simultaneamente. Una rete logica complessa è dunque composta da brevi successioni di porte logiche in cascata che terminano su un latch o su un registro. Il tempo concesso per la propagazione dei segnali attraverso le logiche combinatorie deve essere minore del semiperiodo di clock, in modo che il segnale di ingresso al latch possa raggiungere il suo valore finale in tempo utile per il suo corretto funzionamento, ossia prima che questo passi dalla fase di memorizzazione a quella di valutazione.

I segnali di controllo che regolano il funzionamento di due latch operanti su due sezioni successive della rete devono essere invertiti, in modo che questi operino in controfase. Pertanto, quando un latch entra nella fase di valutazione, quello successivo e quello precedente devono entrare in una fase di memorizzazione, per bloccare la propagazione incontrollata dei segnali. Questa modalità di funzionamento della rete, denominata pipeline nella letteratura inglese, è analoga a quella di una catena di montaggio, nella quale ciascuna sezione compie sempre lo stesso tipo di elaborazione su dati diversi, che si propagano da una sezione all'altra sotto il controllo delle tensioni di clock. Utilizzando questa tecnica nell'esecuzione delle istruzioni di un microprocessore, dopo un breve ritardo iniziale detto latenza, il tempo richiesto per l'esecuzione di un'istruzione diviene equivalente a un solo periodo di clock.

Memorie a semiconduttore

Classificazione

I circuiti di memoria o memorie a semiconduttori, sono quelli preposti alla memorizzazione dei dati e delle istruzioni che controllano l'esecuzione di un programma di calcolo.

La classificazione delle memorie a semiconduttori è rappresentata in fig. 12. Sotto il profilo funzionale, tali memorie si suddividono in due grandi classi: memorie volatili e non volatili. Le memorie volatili sono in grado di conservare l'informazione memorizzata soltanto quando sono connesse all'alimentazione elettrica; per converso, le memorie non volatili conservano l'informazione anche a seguito dello spegnimento dell'apparato nel quale sono inserite. A loro volta, le memorie volatili possono essere ad accesso casuale (RAM, Random Access Memory), ad accesso sequenziale (SAM, Serial Access Memory) o ad accesso per contenuto (CAM, Content Addressable Memory). Le prime sono generalmente preferite per la maggior parte delle applicazioni, in quanto consentono l'accesso diretto all'informazione desiderata in un qualunque indirizzo della memoria. Le memorie ad accesso sequenziale sono viceversa vincolate a una lettura dei dati secondo il loro ordine di memorizzazione, e si prestano pertanto solo per applicazioni particolari che richiedano una lettura sequenziale. Infine, le memorie indirizzabili per contenuto, o memorie associative, sono indirizzate dalla conoscenza del dato e restituiscono l'indirizzo nel quale quel dato è contenuto. Le memorie RAM possono poi essere statiche (SRAM, Static Random Access Memory) o dinamiche (DRAM, Dinamic Random Access Memory), a seconda delle modalità di memorizzazione dell'informazione. Le memorie statiche fanno uso di celle circuitali a due stati stabili e sono in grado di conservare indefinitamente l'informazione finché sono alimentate; al contrario, quelle dinamiche conservano l'informazione sotto forma di carica in una capacità e, a causa delle inevitabili correnti di perdita, richiedono un meccanismo di rigenerazione periodica dell'informazione, o refresh, durante il quale la memoria non può essere interrogata.

Le memorie non volatili possono essere a sola lettura (ROM, Read Only Memory), nel qual caso vengono programmate in modo permanente all'atto della loro fabbricazione; programmabili a sola lettura (PROM, Programmable Read Only Memory), che consentono la programmazione da parte dell'utente mediante un processo irreversibile; programmabili elettricamente (EPROM, Erasable Programmable Read Only Memory), che consentono una programmazione a livello elettrico sul campo, sia pure a prezzo di un maggior tempo di programmazione; infine, programmabili e cancellabili elettricamente (EEPROM, Electrically Erasable and Programmable ROM), che consentono sia la programmazione sia la cancellazione della memoria. Anche in questo caso, la memoria è a sola lettura solo nel senso che il tempo di accesso in lettura è molto minore di quello di programmazione o di cancellazione. Unitamente al loro circuito di decodifica dell'indirizzo, le memorie a sola lettura realizzano un codificatore, nel senso che l'associazione di un dato a M bit a un indirizzo a K bit può essere riguardato come un processo di codifica del dato di ingresso secondo una legge opportuna.

Memorie volatili ad accesso casuale

L'architettura dei moderni calcolatori elettronici fa uso di una gerarchia di memorie che differiscono sensibilmente in tempo di accesso e capacità. Un'elevata velocità di accesso va normalmente a discapito dell'occupazione di area e richiede pertanto una limitata capacità di memoria. Per converso, memorie a elevata capacità sono caratterizzate da elevati tempi di accesso. Ai livelli superiori della gerarchia si trovano i registri e tre livelli di memorie cache, che sono normalmente integrate sullo stesso microcircuito del processore.

Le memorie cache utilizzano tipicamente memorie statiche ad accesso casuale (SRAM) la cui cella base contiene sei transistori. Al livello successivo della gerarchia si hanno memorie dinamiche ad accesso casuale (DRAM) la cui cella di memoria contiene un solo transistore e un condensatore. Ai livelli più bassi della gerarchia si trovano dispositivi di memoria di massa, come i dischi magnetici, i dischi ottici (CD o DVD) e i nastri magnetici, che sono utilizzati soprattutto per l'archiviazione di grandi moli di dati. Importanza crescente stanno anche assumendo le memorie non volatili a semiconduttore di tipo flash, che sono utilizzate per la memorizzazione del programma di accensione dell'elaboratore (BIOS, Basic Input-Output System), nonché per il trasferimento manuale di dati fra elaboratori diversi in sostituzione dei dischi removibili.

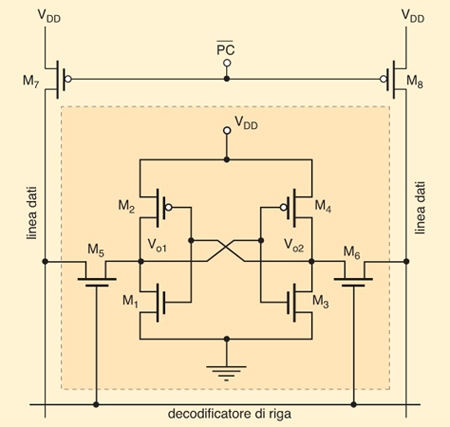

Poiché l'accesso alla memoria rappresenta un vero e proprio collo di bottiglia che limita le prestazioni degli elaboratori, è necessario fare uso di memorie ad alta velocità di accesso sia in lettura sia in scrittura. Soddisfano questo requisito le memorie statiche, la cui cella fondamentale è illustrata in fig. 13. I transistori M1-M4 formano un multivibratore bistabile, i cui nodi di uscita a tensione V01 e V02 sono connessi alle linee dati (bit lines) attraverso i due transistori M5 e M6 operanti come interruttori (pass transistors). I gates di M5 e di M6 sono connessi all'uscita del decodificatore di riga (word line) che indirizza la cella quando la stessa è portata a livello alto e accende i due pass transistors. Le linee dati sono precaricate alte e lasciate in uno stato di alta impedenza: pertanto, la linea dati connessa al nodo che si trova al potenziale di massa, per es., quella di sinistra, comincerà a scaricarsi gradualmente da VDD a 0. La seconda linea dati rimarrà viceversa a VDD, in quanto il nodo corrispondente è polarizzato a VDD e questo mantiene spento M6. Non appena si sviluppa una certa differenza di potenziale fra le due linee dati, questa viene amplificata da un sense amplifier, che genera il livello logico corrispondente al dato rivelato. I tempi di accesso alla memoria statica sono dell'ordine di 1 ns se questa non è troppo grande e se le capacità delle linee di parola e di dato non sono, conseguentemente, troppo elevate.

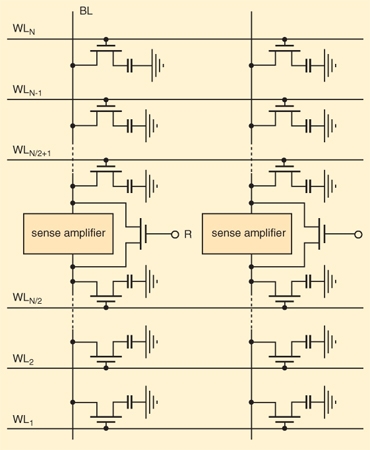

La cella della memoria dinamica è costituita semplicemente da una capacità di memorizzazione connessa a un transistore, che funge da dispositivo di accesso. Il gate del transistore è connesso al decodificatore di linea, mentre il drain del transistore è connesso alla linea dati, come mostrato in fig. 14. La matrice è suddivisa in due parti simmetriche, e le due linee dati sono connesse agli ingressi di un sense amplifier a retroazione positiva che può amplificare la loro differenza di potenziale sino a generare un livello logico all'uscita.

Memorie non volatili flash EEPROM

Le memorie flash EEPROM, o semplicemente flash, hanno avuto il maggior successo commerciale e hanno trovato un'ampia varietà di applicazioni soprattutto nei telefoni cellulari e nelle agende elettroniche.

Le celle flash sono strutturalmente simili a un transistore MOS nel quale si hanno due gates sovrapposti di silicio policristallino. Il gate di primo livello è completamente circondato da ossido di silicio ed è pertanto elettricamente isolato. Il gate di secondo livello è accessibile ed è connesso a una word line. Facendo uso di una tecnica opportuna, che richiede l'applicazione di tensioni insolitamente elevate al gate e al drain della cella, è possibile iniettare elettroni ad alta energia all'interno del gate isolato che, essendo circondato da ossido di silicio, si configura dal punto di vista energetico come una buca di energia potenziale. Gli elettroni iniettati nella regione di gate perdono rapidamente la loro energia cinetica per interazione con il reticolo eccitando vibrazioni reticolari (emissione di fononi) e vengono intrappolati permanentemente nella stessa regione. L'iniezione di elettroni eleva la tensione di soglia VTN del transistore, sino al punto di interdire la cella per valori tipici della tensione di gate normalmente utilizzate in lettura. Pertanto, associando a un transistore spento il valore logico 0 e al transistore acceso il valore logico 1, ciascuna cella potrà memorizzare un bit di informazione.

Le celle flash possono essere cancellate elettricamente per effetto tunnel, un meccanismo di iniezione di natura quantistica che si attiva quando lo spessore della barriera di potenziale che si frappone fra due regioni diviene sufficientemente sottile da consentire alle funzioni d'onda associate ai singoli elettroni di estendersi attraverso la barriera. In pratica, tale iniezione si realizza polarizzando negativamente il gate e positivamente il source, in modo che si sviluppi una differenza di potenziale elevata (14÷16 V) fra questi due terminali. Gli elettroni residenti nel gate isolato sono allora iniettati nella regione di source e la variazione di carica nel gate isolato ne eleva il potenziale elettrico, abbassando la tensione di soglia della cella flash che ripristina la sua programmazione a 1. Lo spessore della barriera di potenziale vista dagli elettroni residenti nel gate, che non coincide con quello dell'ossido, è dovuto all'applicazione di una differenza di potenziale maggiore dell'altezza della barriera (3,2 V) indotta dall'isolante (effetto Fowler-Nordheim).

Un requisito molto importante per le memorie non volatili è la ritenzione dell'informazione per un periodo di almeno 10 anni, sia in condizioni di funzionamento sia a memoria spenta. La probabilità che, in condizioni di equilibrio, un elettrone possa superare per eccitazione termica una barriera di energia potenziale ΔE è proporzionale a exp(−E/kBT), dove kB è la costante di Boltzmann e T è la temperatura assoluta. Poiché kBT∼26 meV a temperatura ambiente e ΔE∼3,2 eV, ne consegue che tale probabilità è assai ridotta. Tuttavia, in presenza di difetti strutturali nell'ossido, o di difetti indotti da intrappolamento di carica positiva, la probabilità di attraversamento dell'ossido da parte di un elettrone per effetto tunnel assistito da trappole può aumentare molto. A causa di ciò, una frazione percentualmente limitata di celle difettive può avere caratteristiche di ritenzione insufficienti. A questo inconveniente si può ovviare prevedendo una certa ridondanza di celle sulla memoria.

Ancora più critica, ai fini della ritenzione dell'informazione, è l'azione di disturbo che viene inevitabilmente compiuta sulle celle non indirizzate dalle operazioni di lettura e scrittura che si compiono su altre celle. Quando si legge, per es., il contenuto di una cella e si alza la word line a VDD e la bit line a VD∼1 V, tutte le celle programmate a 1 e appartenenti alla stessa riga potrebbero subire una sia pur limitata iniezione di elettroni per effetto tunnel nel gate isolato. Tali effetti di disturbo sono ancora più temibili durante le operazioni di programmazione, stante i più elevati valori delle tensioni utilizzate.

Per la realizzazione di un dispositivo di memoria, le celle flash devono essere organizzate in una matrice rettangolare. La matrice può prevedere una configurazione a NOR o una configurazione a NAND. Nel primo caso, le celle appartenenti a una stessa riga condividono la stessa word line e la stessa source line, mentre le rispettive regioni di drain sono connesse a diverse linee dati che attraversano verticalmente la matrice. Nel secondo caso, viceversa, le celle sono connesse fra di loro in serie in numero di 16 o 32, mentre la connessione a massa e alla bit line avviene attraverso due transistori di selezione.

Le flash di tipo NOR sono molto veloci, avendo tempi di accesso in lettura tar∼50 ns. La programmazione della singola cella impiega alcune decine di microsecondi; la cancellazione, seguita dalla riprogrammazione del settore, richiede tempi dell'ordine del secondo. Le flash di tipo NAND si caratterizzano per un'elevata densità e un minor costo per bit rispetto alle flash di tipo NOR, ma hanno tempi di accesso in lettura assai maggiori (tar∼1 μs ). Il parallelismo inerente al funzionamento di un dispositivo di memoria consente, tuttavia, di supplire al tempo di accesso elevato con il trasferimento di grandi blocchi di dati, anziché di dati singoli. Queste differenti proprietà hanno determinato applicazioni diverse per i due tipi di memorie flash: le NOR si prestano, infatti, alla memorizzazione di programmi che debbano essere eseguiti velocemente, mentre le NAND si prestano alla memorizzazione di moli elevate di dati. Lo sviluppo di macchine fotografiche e telecamere digitali, nonché degli standard di telefonia portatile a grande larghezza di banda, hanno favorito un più rapido aumento del mercato delle flash di tipo NAND che, pur essendo state sviluppate da minor tempo, hanno ormai raggiunto la dimensione di mercato delle memorie NOR.